Extra Topics on gem5: KVM and m5 Utility & Memory System

> A presentation by Maryam Babaie

# KVM & m5 Utility

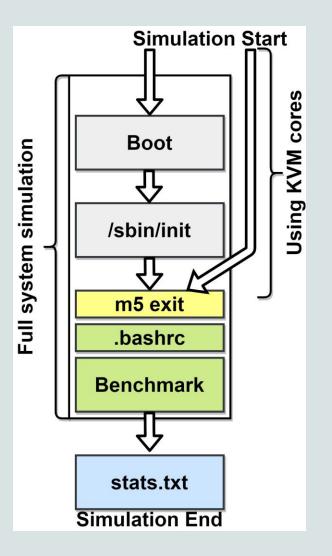

### Fast-forwarding with KVM

- We can <u>fastforward</u> our simulations,

e.g., for the beginning parts that are not within the ROI, like booting.

- gem5 supports switchable CPUs.

- We use **KVM** or **Atomic CPU** to simulate the non-essential regions of the code.

- Then we switch to the desired CPU, e.g., *Timing CPU*.

### m5 Utility

- It provides a command line and library interface for special operations in gem5.

- These operations are requested by the simulated software to perform special behavior which is recognized by gem5 and not the host!

#### m5 Utility Trigger Mechanisms

- Instruction (--inst)

- gem5's CPUs interpret instructions one at a time using gem5's ISA definitions.

- Semihosting

- a mechanism to interrupt normal execution and trigger some sort of behavior in a containing host.

- Address Range (--addr)

- a specially set aside range of physical addresses, to trigger special behavior by gem5

| Trigger         | gem5 Native | KVM |

|-----------------|-------------|-----|

| Instruction     | YES         | -   |

| Semihosting     | ARM         | -   |

| Address         | ARM/X86     | YES |

| <b>⊈</b> 5 gem5 |             |     |

### m5 Utility Trigger: Address Range

- Added for the KVM support of m5 utility.

- It is based on MMIO (memory-mapped IO).

- When a read or write is targeted at that range, instead of a normal device or memory access, a gem5 operation is triggered.

- The default address range starts at 0xffff0000.

- Formatto use: m5 --addr op

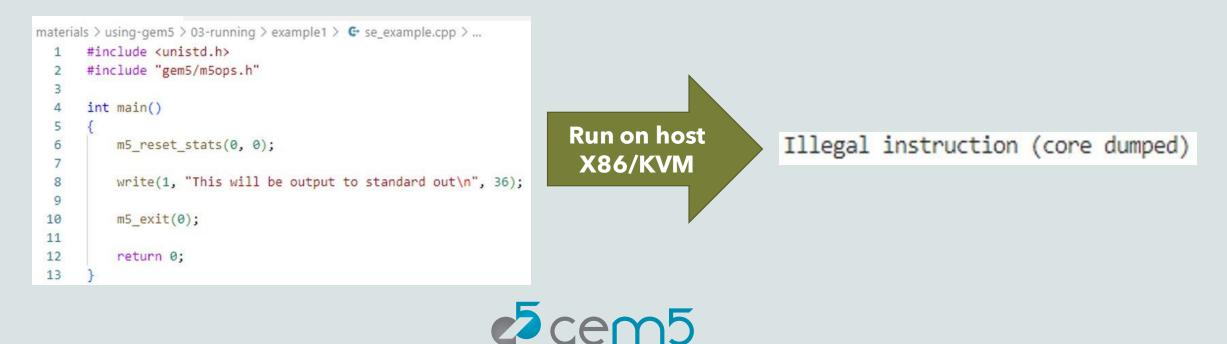

#### m5 Utility + KVM

#### Let's see an example 😳

# Memory System

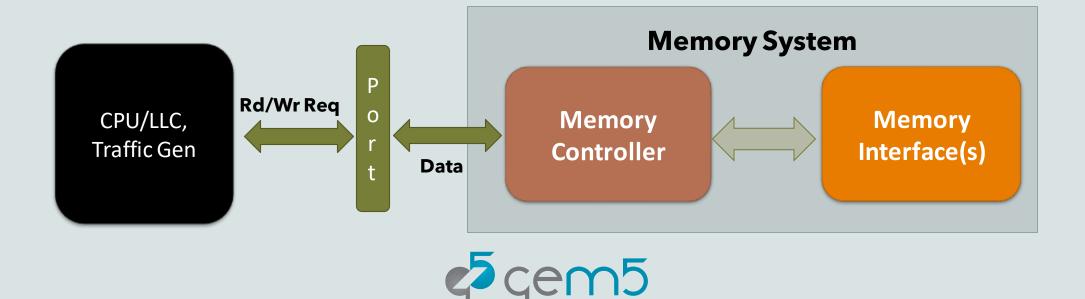

## Memory System

- gem5's memory system is consisted of two main components:

- 1. Memory Controller

- 2. Memory Interface(s)

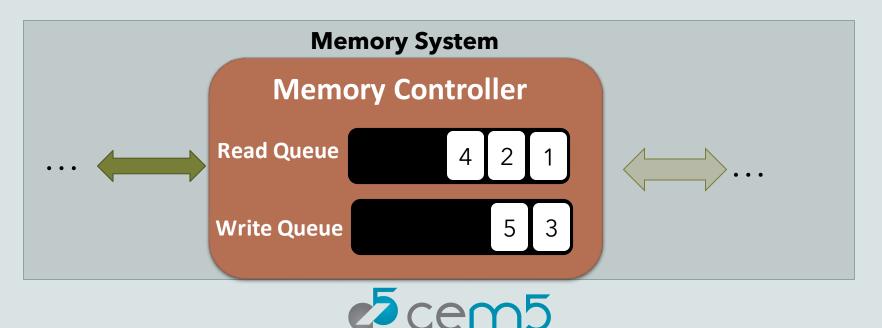

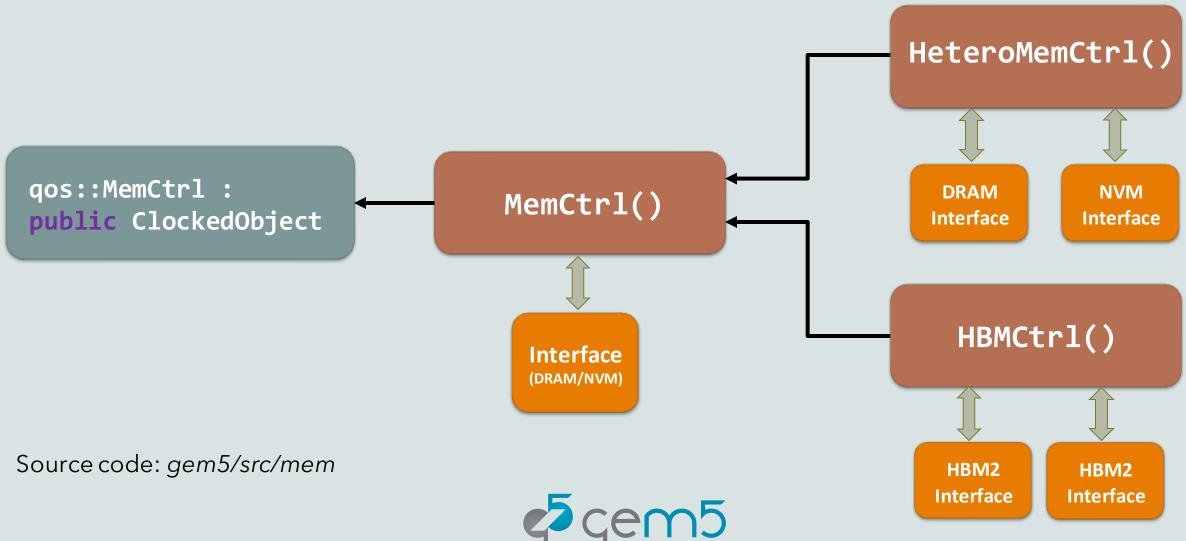

## **Memory Controller**

- Once received the packets, MemCtrlr:

- **enqueues** them into the read and write queues.

- manages the **scheduling algorithm** to issue read and write requests.

- FCFS, FRFCFS

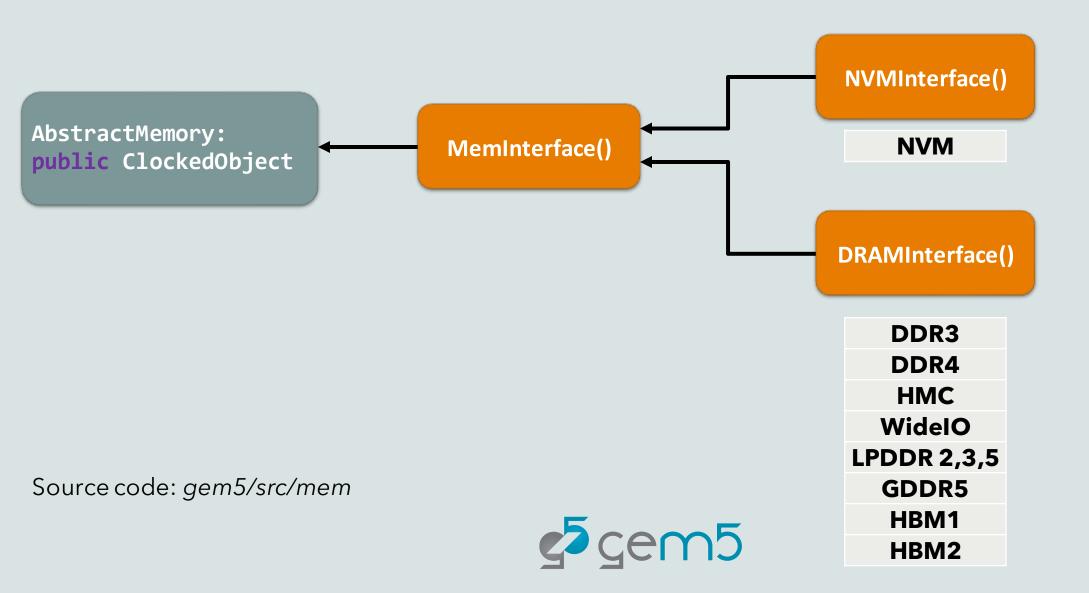

## **Memory Interface**

- The memory interface implements the **architecture** and **timing parameters** of the chosen memory type.

- It manages the media specific operations like activation, pre-charge, refresh and low power modes, etc.

## gem5's Memory Controllers

## gem5's Memory Interfaces

## **Configuring Memory Controllers & Interfaces**

```

from m5.objects import *

from m5.objects import *

1

1

import m5

2

import m5

2

from m5.objects.DRAMInterface import *

3

from m5.objects.DRAMInterface import *

3

from m5.objects.NVMInterface import *

4

from m5.objects.NVMInterface import *

4

5

5

system = System()

6

system = System()

6

system.clk domain = SrcClockDomain()

7

system.clk_domain = SrcClockDomain()

7

system.clk domain.clock = "4GHz"

8

system.clk_domain.clock = "4GHz"

8

system.clk_domain.voltage_domain = VoltageDomain()

9

system.clk domain.voltage domain = VoltageDomain()

9

system.mem mode = 'timing' # 'atomic' or 'functional'

10

system.mem mode = 'timing'

10

11

11

system.generator = PyTrafficGen()

12

system.generator = PyTrafficGen()

12

13

13

system.mem_ctrl = MemCtrl()

14

14

system.mem ctrl = HeteroMemCtrl()

system.mem ctrl.dram = DDR3 1600 8x8(range=AddrRange('8GB'))

15

system.mem ctrl.MemSched = 'fcfs'

15

# system.mem ctrl.dram = NVM 2400 1x64(range=AddrRange('8GB'))

16

16

system.mem ctrl.dram = DDR4 2400 16x4(start='0', end='1GB')

system.mem ctrl.MemSched = 'fcfs'

17

system.mem ctrl.dram.read buffer size = 128

17

system.mem ctrl.dram.read buffer size = 32

18

system.mem_ctrl.nvm = NVM_2400_1x64(start='1GB', end='2GB')

system.mem_ctrl.dram.write_buffer_size = 64

18

19

system.mem_ctrl.nvm.read_buffer_size = 128

19

system.mem_ctrl.dram.device_size = '8GB'

20

system.mem ctrl.dram.tREFI = "56"

system.mem ctrl.nvm.write buffer size = 256

20

21

```

For full list of their configuration options, investigate their Python object files in: gem5/src/mem

# **Configuring Memory Controllers & Interfaces**

```

from m5.objects import *

1

2

import m5

from m5.objects.DRAMInterface import *

3

from m5.objects.NVMInterface import *

4

5

system = System()

6

system.clk domain = SrcClockDomain()

7

system.clk domain.clock = "4GHz"

8

system.clk domain.voltage domain = VoltageDomain()

9

system.mem mode = 'timing' # 'atomic' or 'functional'

10

11

system.generator = PyTrafficGen()

12

13

system.mem ctrl = HBMCtrl()

14

system.mem_ctrl.dram = HBM_2000_4H_1x64(range=AddrRange(start = '0', end = '512MB', masks = [1 << 6], intlvMatch = 0))</pre>

15

system.mem ctrl.dram 2 = HBM 2000 4H 1x64(range=AddrRange(start = '0', end = '512MB', masks = [1 << 6], intlvMatch = 1))</pre>

16

system.mem ctrl.MemSched = 'fcfs'

17

system.mem_ctrl.dram.tREFI = "56"

18

system.mem ctrl.dram 2.read buffer size = 32

19

system.mem ctrl.dram 2.write buffer size = 64

20

```

For full list of their configuration options, investigate their Python object files in: gem5/src/mem

## Thank you!